Desarrollando con Vitis HLS - Sesión 1 - Introducción.

- ¿Qué es Vitis HLS?

Vitis HLS es un poderosa herramienta utilizada para sintetizar una función escrita en lenguaje C/C++ en código RTL. El cual por definición puede ser implementado en una región PL disponible en arquitecturas de hardware reconfigurable como las Versal ACAP, ZYNQ, MPSoC o Xilinx FPGA. Esta herramienta viene incluida en el instalador del software Vivado de Xilinx y permite la escritura, depuración del lenguaje C/C++, síntesis y simulación tanto en la etapa del programa C/C++ como en el resultado de la síntesis garantizando una evaluación previa al proceso de la creación del componente. El resultado final es un Ip Core escrito en código verilog o VHDL según se ajuste en la configuración de "EXPORT RTL" cuyas entradas y salidas están definidas por las variables que representan los parámetros de la función denominada "Top Function" las cuales se convertirán entradas/salidas en función de como sean declaradas. Además, al momento de la síntesis, el hardware incorpora otras variables las cuales por lo general son banderas que representan el estado de ejecución de la función una vez implementada en hardware. A continuación, Estos son los pasos para el desarrollo de la función C++. - Diseñar el algoritmo basado en los Principios de Diseño

- (C-Simulación) Verifique el código C/C++ con el banco de pruebas C/C++

- (C-Síntesis) Genere el RTL usando HLS

- (Co-Simulación) Verificar el kernel generado con salidas de C++

- (Analizar) Revisar los informes de síntesis HLS y los informes de cosimulación, analizar

- Vuelva a ejecutar los pasos anteriores hasta alcanzar los objetivos de rendimiento.

- Aplicaciones del Vitis HLS y la Top Function.

Por simple inspección, la aplicación de Vitis HLS parecer ser muy clara, escribir un lenguaje C/C++ y llevar ese programa a su equivalente en Verilog o VHDL lo cual permitiria desarrollar hardware con un lenguaje mas conocido por todos como son los programas en C respecto del lenguaje descriptor de hardware. Sin embargo, la aplicación va mas allá de eso, a la hora de describir una arquitectura de hardware es importante explotar el paralelismo del cual disponen las arquitecturas de hardware reconfigurables. Por tanto, la plataforma viene acompañada de una serie de directivas PRAGMA para desenrollar bucles que no sean dependientes entre ellos, separación de arreglos en diferentes bloques de memoria, sub funciones de bloques superior para formar una jerarquía del diseño RTL. Entre otras herramientas que mejoran el diseño y optimizan los recursos de hardware en la creación del componente.

Ahora hablaremos de la Top Function. Sabemos que al programar en lenguaje C existe una función muy popular llamada "Main" y es la función principal que ejecuta el compilador de C. Sin embargo, para nuestro caso se tiene una función con el nombre que nosotros decidamos, pero es muy importante definir dicha función como "Top Function" a la hora de crear el proyecto ya que los argumentos de dicha función pasarán a convertirse en los puertos de entradas y salidas del componente que se creará. en la siguiente imagen se puede apreciar que, en términos de jerarquía la top function ostenta el puesto mas alto y de ella se mandan a llamar cualquier otra función para desarrollar sub procesos.

En la imagen puede ver un programa en C/C++ compuesto por las funciones A, B, C y D y una Top Function donde se manda a llamar funciones que están fuera y estas llaman a otras funciones de más fuera dando lugar a una jerarquía de ejecución. - Desarrollo de un programa en lenguaje C.

Hemos hablado sobre que es Vitis HLS y su funcionamiento el cual parte de la generación de un archivo codificado en C/C++ cuya función principal no esta dada precisamente por la convencional función "Main". Para nuestro caso crearemos un proyecto muy sencillo que nos permita conocer un poco la estructura que debe llevar la Top Function y algunas consideraciones necesarias para el diseño en Vitis HLS desde el momento que comenzamos a escribir el código en C/C++.

En el siguiente ejemplo, creamos un archivo de C++ y un archivo de cabecera. Estos programas serán utilizados para crear una componente en VHDL cuyo objetivo será sumar 2 números contenidos en 2 palabras de 8 bits y generar un resultado en una palabra de 8 bits.

Primero examinamos el archivo de cabecera donde se genera una constante de nombre N a la cual se le asigna el valor de 2. Luego, se define un tipo de dato, esto sirve para definir ubicar mas fácilmente los tipos de datos que deseamos manejar en el componente. y finalmente, se define la función con los parámetros que se le deben pasar a dicha función con miras puestas en que, estos parámetros se convertirán en los puertos de entrada y salida del componente que se implementará en nuestra FPGA. A continuación, vemos el archivo escrito en lenguaje C.

Como se observa el código en C, no hay mucho que concluir, a simple vista el algoritmo de programación se basa en la suma de dos variables de tipo "TD" las cuales son variables tipo char, es decir, de un byte y su resultado es pasado al puntero nombrado "dato3". - Desarrollo de un proyecto en HLS.

Ahora, comenzaremos con la creación de un proyecto en Vitis HLS cuya implementación es muy simple. Básicamente es un paso a paso como se ve a continuación.

A continuación, se muestra la ventana de inicio del Vitis HLS, para crear un proyecto nuevo hacemos click sobre la columna "Project" en la opción Created Project. Luego se abrira una ventana en la cual se puede ajustar el nombre y el directorio con el cual se creará y guardará el proyecto.

Una vez realizado el paso anterior el proyecto solicitará incluir los archivos C/C++ como se muestra a continuación.

Haga click sobre el botón "Add Files..." he incluya los archivos .C y .h generados al inicio de la guía de usuario, luego haga click sobre el botón "Browse" con esta opción y automaticamente le permitirá seleccionar la Top Function dando como alternativas el titulo de las funciones que se encuentren declaradas en el código, como se podrán recordar, el nombre de la función generada en C lleva por nombre "Ope". A continuación vea la ventana de opciones para seleccionar la top function.

Por ultimo el proyecto pedirá seleccionar el chip con el cual se va a trabajar para, para mi caso particular utilizaré el chip xc7a35t-csg324-1 que viene en la FPGA Artix-7, hacemos click en finalizar y todo estará listo para lanzar el proyecto en Vitis HLS. - Síntesis del proyecto en HLS y verificación del reporte generado por el RTL.

A continuación, se abrirá el entorno de desarrollo de Vitis HLS, note que en la parte inferior se encuentra la consola con la información que arroja la herramienta en cada uno de sus pasos, en la parte izquierda tenemos el explorador del proyecto, allí, en la carpeta source encontrará los archivos .c y .h.

Al hacer click en los archivos de código fuente vera como se despliegan en la pantalla los cuales pueden ser verificados y compilados. Sin embargo, realizamos el proceso de síntesis, para esto, en la parte izquierda se tiene la opción de "flow navigator" donde podrá ver la pestaña C synthesis y dentro se encuentra la opción "Run C synthesis". Realice la ejecución y espere a que finalice, luego el sistema le mostrará en la pantalla principal el reporte del componente RTL que se implementará cuando realice la exportación. A continuación se muestra el reporte.

En el reporte se puede apreciar la cantidad de LUT, BRAM, Latencia, DSP. Al ser un proyecto con una operación relativamente simple no demanda mayor cantidad de recursos y luego tenemos la Top Function Arguments donde se pueden apreciar los argumentos con una dirección asignada como puede ser entrada o salida y mas abajo declarados ya como puertos. Si todo esta acorde a como queremos, estamos listos para crear el Ip Core que exportaremos al catalogo de Ip Core. - Creación del Ip Core con el componente desarrollado en lenguaje C/C++.

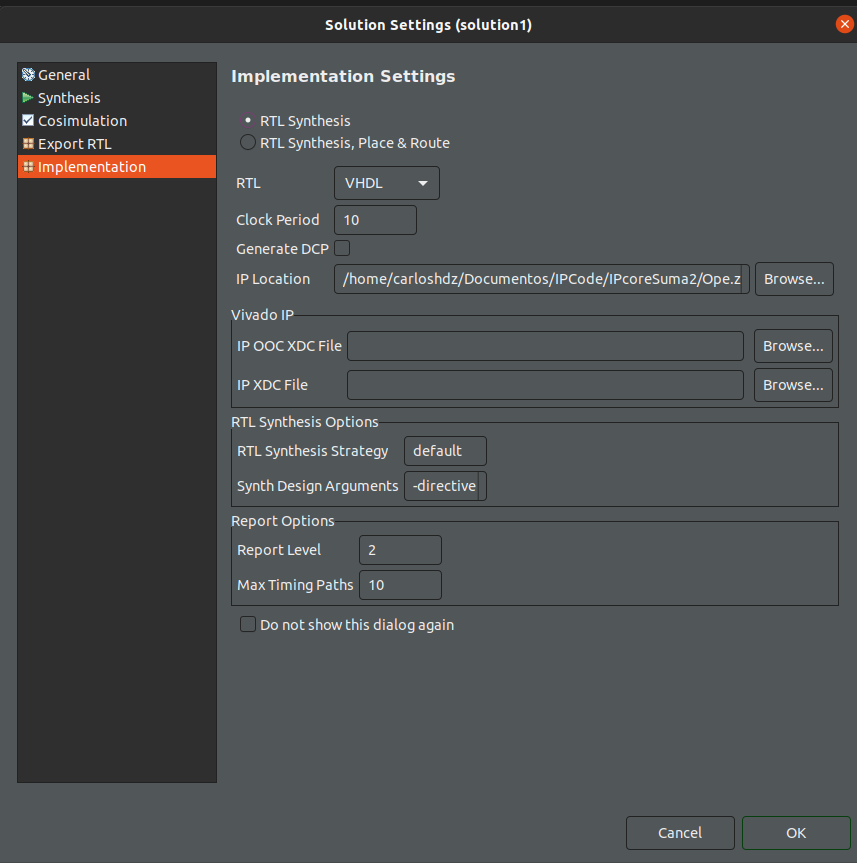

Como paso final tenemos la implementación del Ip Core que será exportado. en el paso anterior es importante verificar que el diseño del componente este lo mas automatizado posible en cuanto a recursos de hardware, una vez garantizado, abrimos la configuración del proyecto. A continuación, vea la siguiente imagen.

Es muy importante que seleccione en el RTL el lenguaje al cual quiere exportar el componente y la localidad a donde pretende guardar su Ip Core. Por ultimo, vaya nuevamente al Flow navigator y en la pestaña "IMPLEMENTATION" seleccione Export RTL y se desplegará la siguiente ventana.

Es muy recomendable que añada la ubicación y exporte el Ip Core, de preferencia a un .zip, y en Ip Configuration es recomendable realizar una descripción del Ip Core ya que eso será exportado al catalogo de Ip Core junto con el componente creado. - Bibliografía.

- https://docs.xilinx.com/r/en-US/ug1399-vitis-hls/Introduction-to-Vitis-HLS

- Vitis High-Level synthesis user guide

- https://www.youtube.com/watch?v=5lYq8_bqAcI&t=378s

Comentarios

Publicar un comentario